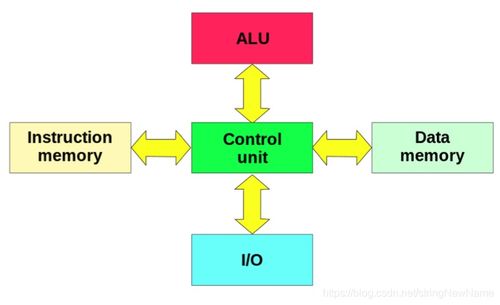

計(jì)算機(jī)硬件開發(fā)是一個(gè)復(fù)雜而系統(tǒng)的工程,涉及從底層邏輯電路到上層軟件應(yīng)用的多個(gè)層次。《計(jì)算機(jī)組成與設(shè)計(jì):硬件/軟件接口》的RISC-V版為這一領(lǐng)域提供了重要的理論基礎(chǔ)和實(shí)踐指導(dǎo)。本書以開源的RISC-V指令集架構(gòu)為核心,系統(tǒng)地闡述了計(jì)算機(jī)硬件與軟件之間的交互機(jī)制,為現(xiàn)代計(jì)算機(jī)硬件開發(fā)提供了清晰的技術(shù)路線。

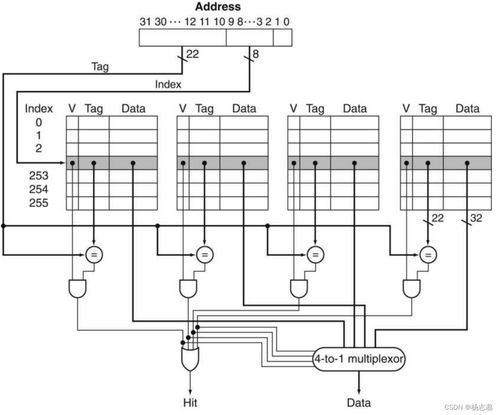

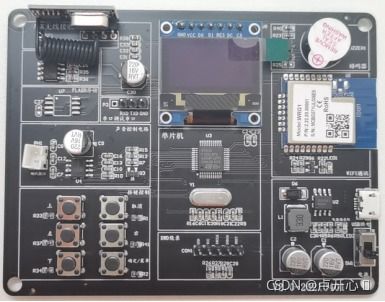

RISC-V作為一種精簡、模塊化且開源的指令集架構(gòu),正逐漸成為計(jì)算機(jī)硬件開發(fā)的熱門選擇。與傳統(tǒng)指令集相比,RISC-V的設(shè)計(jì)更加簡潔高效,允許開發(fā)者根據(jù)具體需求進(jìn)行定制化擴(kuò)展。這種靈活性使得RISC-V在嵌入式系統(tǒng)、物聯(lián)網(wǎng)設(shè)備、高性能計(jì)算等多個(gè)領(lǐng)域展現(xiàn)出巨大潛力。本書通過詳細(xì)解析RISC-V的指令集、流水線設(shè)計(jì)、內(nèi)存層次結(jié)構(gòu)等關(guān)鍵組件,幫助讀者深入理解硬件與軟件協(xié)同工作的原理。

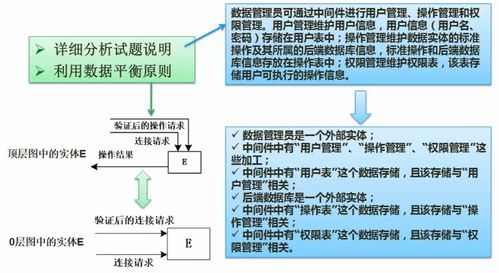

在計(jì)算機(jī)硬件開發(fā)中,硬件/軟件接口的設(shè)計(jì)至關(guān)重要。接口定義了硬件如何響應(yīng)軟件指令,以及軟件如何有效利用硬件資源。RISC-V架構(gòu)通過明確的規(guī)范,確保了不同硬件實(shí)現(xiàn)之間的兼容性,降低了開發(fā)門檻。本書通過實(shí)例分析,展示了如何基于RISC-V設(shè)計(jì)處理器核心、內(nèi)存系統(tǒng)和外設(shè)接口,并探討了優(yōu)化性能與能效的策略。例如,書中詳細(xì)介紹了流水線冒險(xiǎn)的處理、緩存一致性的實(shí)現(xiàn)以及多核處理器的同步機(jī)制,這些內(nèi)容對實(shí)際硬件開發(fā)具有直接的指導(dǎo)意義。

RISC-V的開源特性促進(jìn)了硬件開發(fā)的創(chuàng)新與協(xié)作。開發(fā)者可以自由訪問和修改設(shè)計(jì),加速了從概念到產(chǎn)品的轉(zhuǎn)化過程。本書還涵蓋了硬件描述語言(如Verilog)的使用,以及仿真與測試方法,為讀者提供了完整的開發(fā)工具鏈知識(shí)。通過結(jié)合理論講解與實(shí)戰(zhàn)案例,讀者不僅能夠掌握計(jì)算機(jī)組成的基本原理,還能獲得動(dòng)手開發(fā)RISC-V兼容硬件的實(shí)踐能力。

《計(jì)算機(jī)組成與設(shè)計(jì):硬件/軟件接口》的RISC-V版是計(jì)算機(jī)硬件開發(fā)領(lǐng)域的重要參考資料。它以開源架構(gòu)為切入點(diǎn),深化了我們對硬件/軟件交互的理解,并為未來的技術(shù)創(chuàng)新奠定了堅(jiān)實(shí)基礎(chǔ)。隨著RISC-V生態(tài)的不斷發(fā)展,掌握其核心知識(shí)將成為硬件開發(fā)者的關(guān)鍵競爭優(yōu)勢。